Computational Hardware Accelerators for Robotics

Computational Hardware Accelerators for Robotics

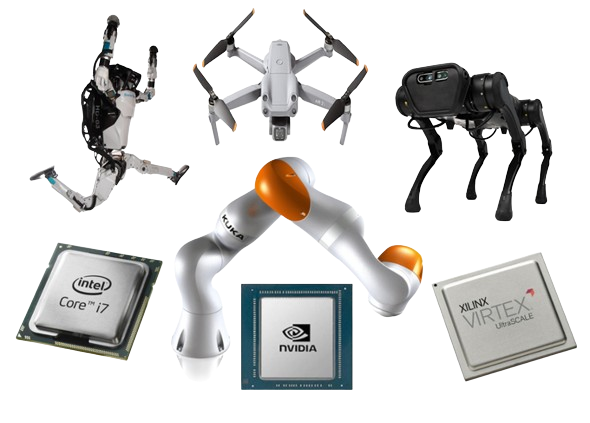

Project Overview

Computer architects have shown that moving beyond the CPU and GPU, to custom computational hardware, can further accelerate computations while lowering energy consumption. How can we apply these techniques in robotics? This project seeks to answer that question through the design of automated workflows that can directly encode into computational hardware the structured sparsity and parallelism patterns found in embodied robotics algorithms. These resulting co-designed FPGAs and custom ASICs can then be flexibly leveraged for downstream robotics applications.

Publications

-

(2025). MPC Solver Hardware Generation Framework with Model-Specific Operation Fusion and Pruning. In ICFPT 2025.

-

(2022). GPU Acceleration for Real-time, Whole-body, Nonlinear Model Predictive Control. Harvard University PhD Dissertation.

-

(2021). Robomorphic Computing: A Design Methodology for Domain-Specific Accelerators Parameterized by Robot Morphology. In ASPLOS 2021.

IEEE Micro Top Picks 2022 Honorable Mention

-

(2019). Application of Approximate Matrix Multiplication to Neural Networks and Distributed SLAM. In HPEC 2019.